ٴ[Discontinued] VP460 RFSoC Board

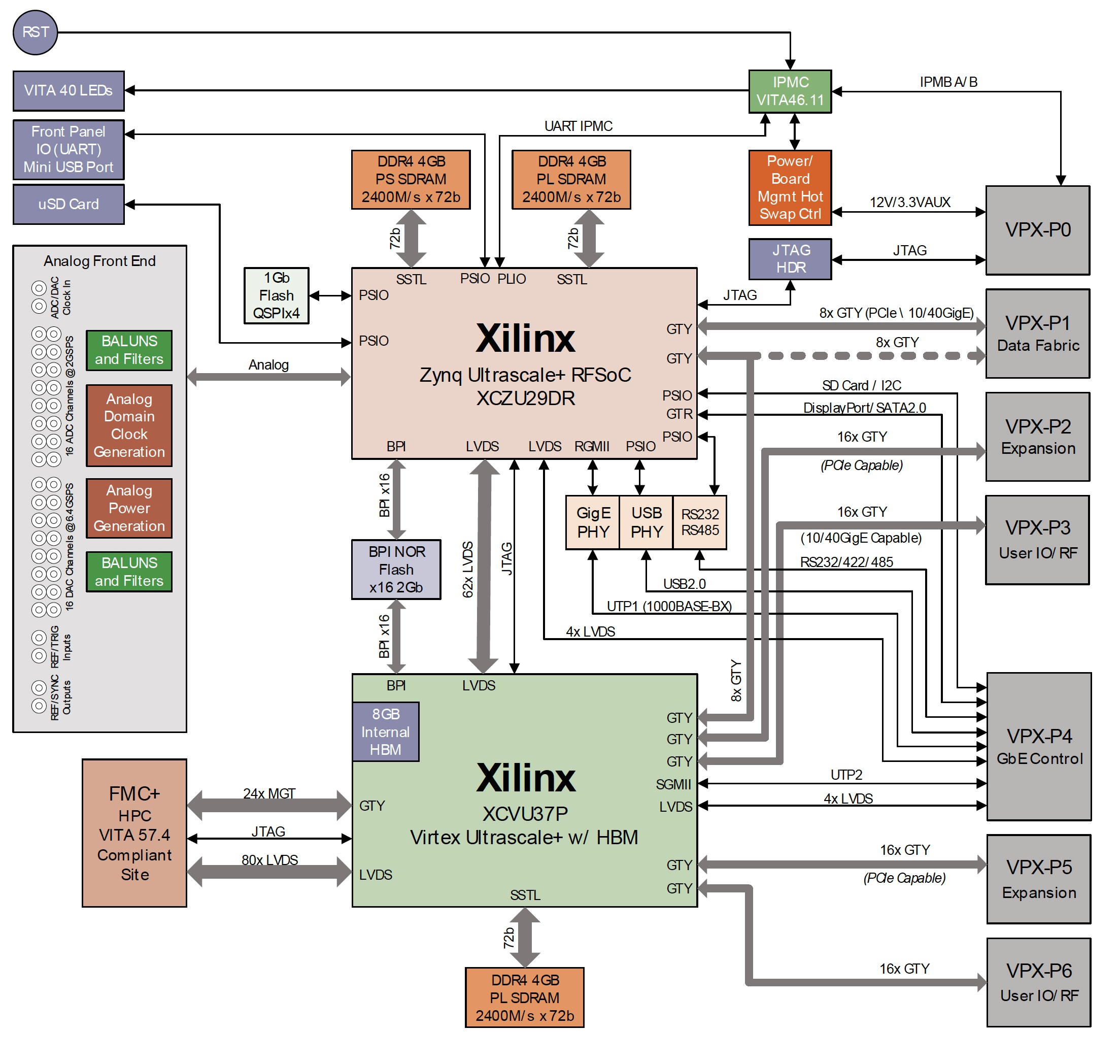

The VP460 is a 6U VPX RF processing system featuring the Xilinx® Zynq® Ultrascale+™ RF system-on-chip technology (RFSoC) and the latest Xilinx Virtex™ Ultrascale+ High Bandwidth Memory (HBM) FPGA device.

The RFSoC ZU29DR device used on the VP460 includes 16 integrated analog-to-digital converters at 2GSPS, 16 digital-to-analog converters at 6.4 GSPS, a user-programmable FPGA fabric, and multi-core Zynq ARM® processing subsystem. The HBM VU37P device features the speed and capabilities of an UltraScale+ FPGA plus integrated DRAM in the FPGA package capable of up to 460GB/s data transfer rates on -chip.

- Reduced RF Signal Chain Complexity

- VP460 enables direct RF sampling which can be implemented in the digital domain, bringing greater flexibility and simplification to the signal processing chain

- Maximise Input/Output Channel Density

- VP460 has the ability to synchronise all 16 channels as well as multiple boards for even larger system applications

- Revolutionary processing capability

- VP460 perfectly balances the need for high performance FPGA processing, the ease of a hardened embedded processor and the ultra-low latency of integrated analog interfaces. This enables users to create advanced multi-channel electronic warfare systems, radar, and SDR applications.

- Offload Data More Efficiently

- In addition to the PCIe Gen3 data plane, VP460 includes up to 48 high speed serial lanes to the Xilinx Virtex Ultrascale+ HBM device supporting protocols such as PCIe Gen3, 10G Ethernet, Aurora, etc.

- Dual FPGA Architecture:

- Zynq UltraScale+ RFSoC

- Virtex UltraScale+ HBM

- ADC 16 channels 2 GSPS 12-bit

- DAC 16 channel 6.4 GSPS 14-bit

- Independent clock generation circuit for the ADC and DAC front ends

- Application Processing Unit

- Quad-core ARM Cortex-A53

- Real-Time Processing Unit

- Dual-core ARM Cortex-R5

- Up to 8 GB DDR4 memory available to the RFSoC

- Up to 12 GB DDR4 memory available to the Virtex UltraScale+

- 8 GB integrated on the device

- Up to 460 GB/s transfer rates with integrated DRAM

- VITA 57.4 FMC+ site available to the Virtex UltraScale+ HBM

- PCIe Gen3 x 16 from HBM to the backplane and x8 from the RFSoC

- Low latency, high bandwidth parallel data bus between the Zynq UltraScale+ RFSoC and Virtex UltraScale+ HBM devices

- User I/O to backplane RTM

- DisplayPort™ 1.2a

- SATA 3.1

- USB 3.0

- Gigabit Ethernet

- Linux® and Windows® BSP available

- SOSA Backplane Option