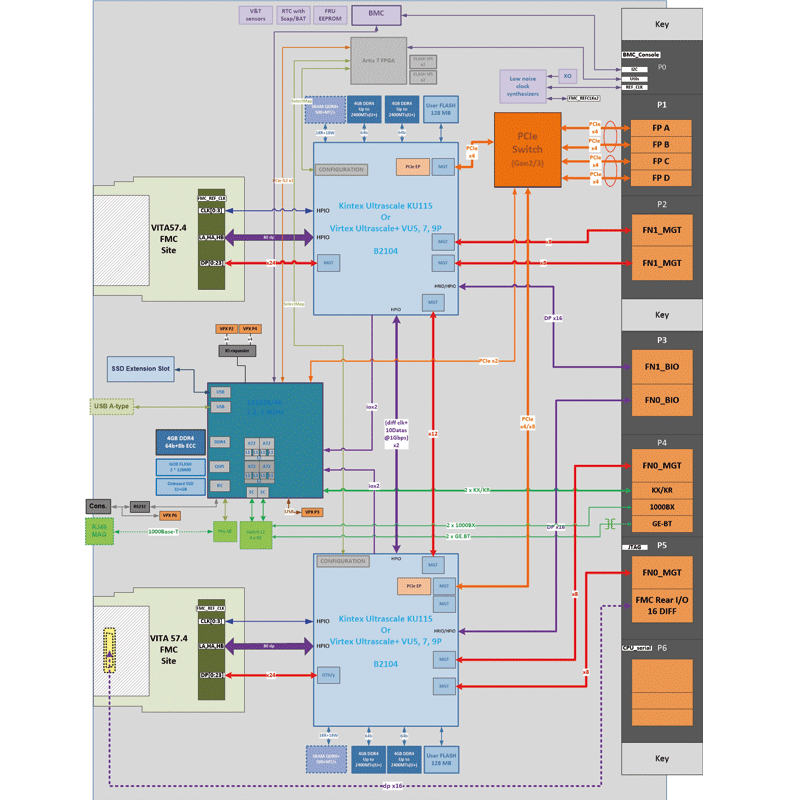

IC-FEP-VPX6e – 6U VPX FPGA board with two FMC+ sites

Based on the latest Xilinx 20nm FPGA family, the IC-FEP-VPX6e enhances the Front-End Processing (FEP) Interface Concept product line.

By offering a higher performance/power consumption ratio compared to previous FPGAs, the UltraScale™ FPGAs make the IC-FEP-VPX6e the perfect solution to applications requiring DSP intensive processing in a 6U VPX form factor.

The IC-FEP-VPX6e together with other IC building blocks (Intel® and PowerPC SBCs, Ethernet Switches & Routers, FMC) running our Signal Processing Reference Design are the ideal platforms for customers who

want to streamline development by concentrating their efforts on their most strategical tasks.

Features

- QorIQ® LS1046A – quad 64-bit Arm Cortex®-A72 cores @1.8 GHz:

- 4 GB DDR4 ECC

- 2 * 1Gbit QSPI Flash

- on board SSD (32GB), eMMC

- optional Nand Solid-state Disk (eUSB module)

- Two Kintex® UltraScale™ KU115, Virtex® UltraScale™/ UltraScale+™, both offering :

- Two banks of DDR4 : 64-bit wide, up to 4GB each

- QDRII SRAM

The two FPGAs are interconnected:

- directly via 12 GTY lanes and 24 differential pairs

- via the Gen2/3 PCIe switch

VPX Interfaces

- 4 * PCIe x4 ports or 2* PCIe x8 ports (from the PCIe switch)

- GTH ports (2 * GTH x8 from each FPGA)

- General purpose IOs

- 16 differential pairs each FPGA

- 16 differential pairs from one FMC IOs connector (option)

- GPIOs (from ctrl node FPGA)

- 2 * 10GigaBase-KR (or 1000BaseKX) from the processor

- 2 * 1000BaseKX and 2 * 1000BaseBT ports from the switch

- 1 * RS232 port

- 1 * USB 2.0 port

- PIC µ-controller for System Management (per VITA 46.11)

FMC+ interfaces (HSPC for each FPGA site)

- 80 * differentials pairs

- 4 * reference clocks

- 24 * GTH/Y lanes

Front Panel Interfaces

- 1 * USB 2.0, 1 * Ethernet 1000BaseT and 1 * console port.