IC-FEP-VPX3f – 3U VPX VITA 66.5 FPGA board with FMC+ Site

Based on the latest Xilinx 20nm FPGA family, the IC-FEP-VPX3f enhances the front-end processing (FEP) product line of Interface Concept as the first VITA 66.5 compliant FPGA board on the market today.

The IC-FEP-VPX3f and other IC building blocks (Intel ® and PowerPC SBCs, Ethernet Switches & Routers, FMC) running IC’s Signal Processing Reference Design, are ideal platforms for users wishing to streamline development and concentrate their efforts on core strategic tasks.

Features

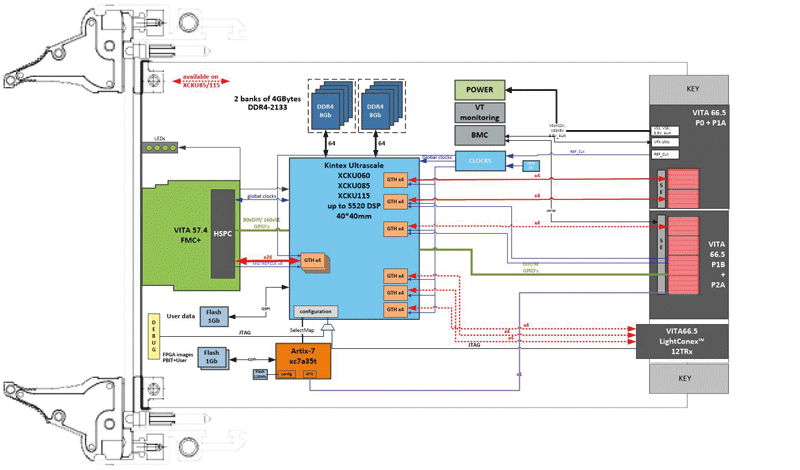

- Kintex® UltraScale™ KU060, KU85 or KU115

- Two banks of DDR4: 64-bit wide, up to 4GB each

- 2 * 128 MBytes of QSPI flash (bitstreams storage)

- 1 * 128 MBytes of QSPI flash (User Data storage)

VPX Interfaces

- Up to three 4-lane fabric ports on P1/P2

- 3 * GTH x4 (Fat Pipes P1A, P1B) (*)

- Optional 3 * GTH x4 to LightConex™ 12TRX (*)

- 28 GPIO’s from FPGA on P2, usable as single-ended or differential pairs

(*) depending on FPGA models

FMC+ VITA 57.4 interfaces

- 6 GTH x4 links

- 80 differential pairs

- 6 reference clocks

- Engineering kit : JTAG ports for direct FPGA configuration

- Rear Transition Module