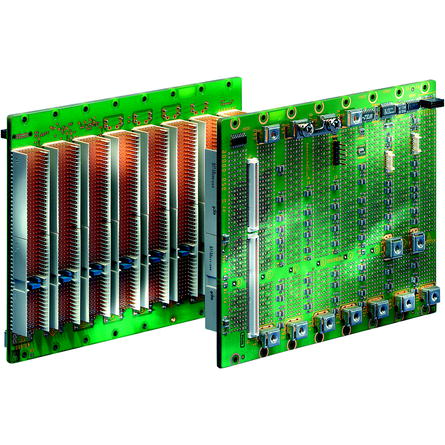

PXI backplanes

- 12-layer structure, min. crosstalk digital to analog section

- In accordance with:

- PXI Specification R 2.0

- PICMG 2.0 R3.0 CompactPCI Core Specification

- PICMG 2.1 R2.0 Hot-swap Specification

- PICMG 2.9 R1.0 System Management Bus Specification

- PICMG 2.10 R1.0 Keying Specification

- 64-bit CompactPCI bus and PXI bus on the P2 plane

- Clock generated on the backplane; feeding in an external clock is possible, the backplane switches automatically between the two clocks

- Backplanes with up to 5 slots are capable of 66 MHz, 6 to 8 slot backplanes are set to 33 MHz operation

- Outstanding high-frequency noise suppression and very high MTBF values due to ceramic capacitors

- Utility connector for status signals

- Intelligent platform management bus (IPMB) connector to PICMG 2.9