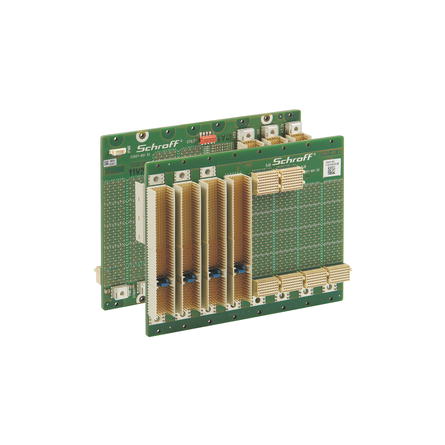

CompactPCI PlusIO backplanes

CompactPCI PlusIO backplanes

- In accordance with:

- PICMG 2.0 R3.0 CompactPCI Core Specification

- PICMG 2.1 R2.0 Hot-Swap Specification

- PICMG 2.9 R1.0 System Management Bus Specification

- PICMG 2.10 R1.0 Keying Specification

- PICMG 2.30 R1.0 CompactPCI PlusIO specification

- PICMG CompactPCI Serial (CPCI-S.0 R1.0) specification

- System slot in accordance with PICMG 2.30, 32-bit CPCI bus on P1, PCIe, S-ATA, USB & Ethernet on P2

- CompactPCI peripheral slots, 32 bit with rear I/O on P2

- CompactPCI Serial peripheral slots with PCIe x1, S-ATA and USB

- Full-mesh Ethernet on system slot and 2 CompactPCI Serial slots, supports 1000Base-T and 10GBase-T

- Rear I/O on the CompactPCI Serial slots available on request

- V(I/O) can be set to 3.3 V or 5 V (preset to 5 V)